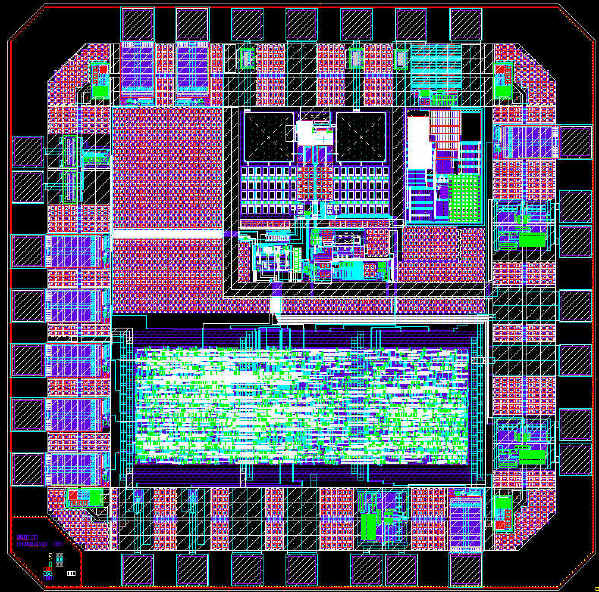

The QPLL ASIC is a Phase-Locked Loop based on a Voltage Controlled Quartz Crystal Oscillator (VCXO). Its function is to act as a jitter-filter and clock multiplier for clock signals operating at the LHC bunch-crossing frequency (40.08 MHz). The device is implemented in a 0.25 mm CMOS technology using radiation tolerant layout practices. It is conceived to meet the LHC radiation requirements.

Technical contact: Paulo Moreira

Last update: 12/01/2005 - If you want to be included in a QPLL mailing list please let me know.